방통대1/컴퓨터구조

처리장치(1)

book_lover

2024. 3. 15. 07:15

처리장치의 개요

- 중앙처리장치(CPU, Central Processing Unit)

처리 장치와 제어 장치가 결합된 형

https://hongcoding.tistory.com/139 - 제어장치 : 연산의 실행순서를 결정, 처리장치에 제어신호 보냄

- 처리장치 : 데이터를 처리하는 연산을 실행, 제어장치에 생태신호 보냄

[1]클럭(clock): 연산 작업을 위해 0 또는 1의 전기적 진동을 지속적으로 생성하는 것. Hz(헤르츠) 단위로 표기하며, 기본적으로 클럭 수치가 높을수록 처리 속도가 빠르다는 의미

[2]IPC(Instructions Per Cycle): 클럭 당 명령어 처리 횟수. 명령어 하나를 처리하는데 클럭이 얼마나 필요한지를 측정하므로CPU가 얼마나 효율적으로 작동하는지를 평가하는 단위

[3]코어(core): CPU 내부에 있는 물리적인 처리 회로의 핵심 부분. 코어 개수가 많을수록 여러 가지 작업을 동시에 수행하는데 유리. 코어가 1개면싱글코어, 2개면 듀얼코어, 4개면 쿼드코어, 6개면 헥사코어, 8개면 옥타코어 등으로 말함

[4]슈퍼스칼라(superscalar): 파이프라인과 병렬 처리의 장점을 모은 것으로, 여러 개의 파이프라인에서 명령들이 병렬로 처리되도록 한 아키텍처. 여러 명령어들이 대기 상태를 거치지 않고 동시에 실행될 수 있으므로 처리속도가 빠름

[5]디버깅(debugging): 설계된 프로그램을 확인하고, 프로그래밍 상의 오류를 찾아 고치는 작업

[6]RTL(Register Transfer Level): 디지털 회로 설계의 첫 단계로 일종의 소스코드

출처 : ‘엑시노스’ 개발 리더들이 SoC를 말하다] ② CPU · NPU 알아보기

처리장치의 구성

▶ ▶ ▶ 산술논리연상장치와 레지스터들로 구성

- 산술논리연산장치(ALU, Arithmetic and Logic Unit)

- 산술, 논리, 비트연산 등의 연산을 수행

- 레지스터(Register)

- 연산에 사용되는 데이터나 연산의 결과를 저장

산술논리연산장치는 독립적으로 데이터를 처리하지 못하며, 반드시 레지스터들과 조합하여 데이터를 처리

마이크로 연산

▶ ▶ ▶ 레지스터에 저장되어 있는 데이터에 대해 이루어지는 기본적인 연산

마이크로 연산의 종류

- 레지스터 전송 마이크로 연산

- 산술 마이크로 연산

- 논리 마이크로 연산

- 시프트 마이크로 연산

레지스터의 표현

레지스터 전송 마이크로 연산

한 레지스터에서 다른 레지스터로 2진 데이터를 전송하는 연산

- 레지스터 사이의 데이터 전송은 "연산자 ←"로 표시

- R2 ← R1

- 의미 : 레지스터 R1의 내용을 R2로의 전송

※ 하드웨어적인 측면에서 레지스터 전송

- 조건문 표현

- if (T1 = 1) then (R2 ← R1)

- 레지스터 전송문 표현

- T1 : R2 ← R1

※ 레지스터 전송문장에서 사용되는 기본적인 기호

- 영문자(숫자와 함께) 레지스터를 표시

- AR, R2, DR, IR

- 괄호 : 레지스터의 일부분

- R2(1), R2(7:0), AR(1)

- 화살표 : 자료의 이동 표시

- R2 ← R1

- 쉼표 : 동시에 실행되는 두 개 이상의 마이크로 연산을 구분

- R1 ← R2, R2 ← R1

- 대괄호 : 메모리에서의 어드레스(Adress)

- DR ← M[AR]

산술 마이크로 연산

레지스터 내의 데이터에 대해서 실행되는 산술연산

기본적인 산술연산으로는 덧셈, 뺄셈, 1 증가, 1 감소, 그리고 보수연산이 있다.

논리 마이크로 연산

레지스터 내의 데이터에 대한 비트를 조작하는 연산

시프트 마이크로 연산

레지스터 내의 데이터를 시프트 시키는 연산

데이터의 측면이동에 사용

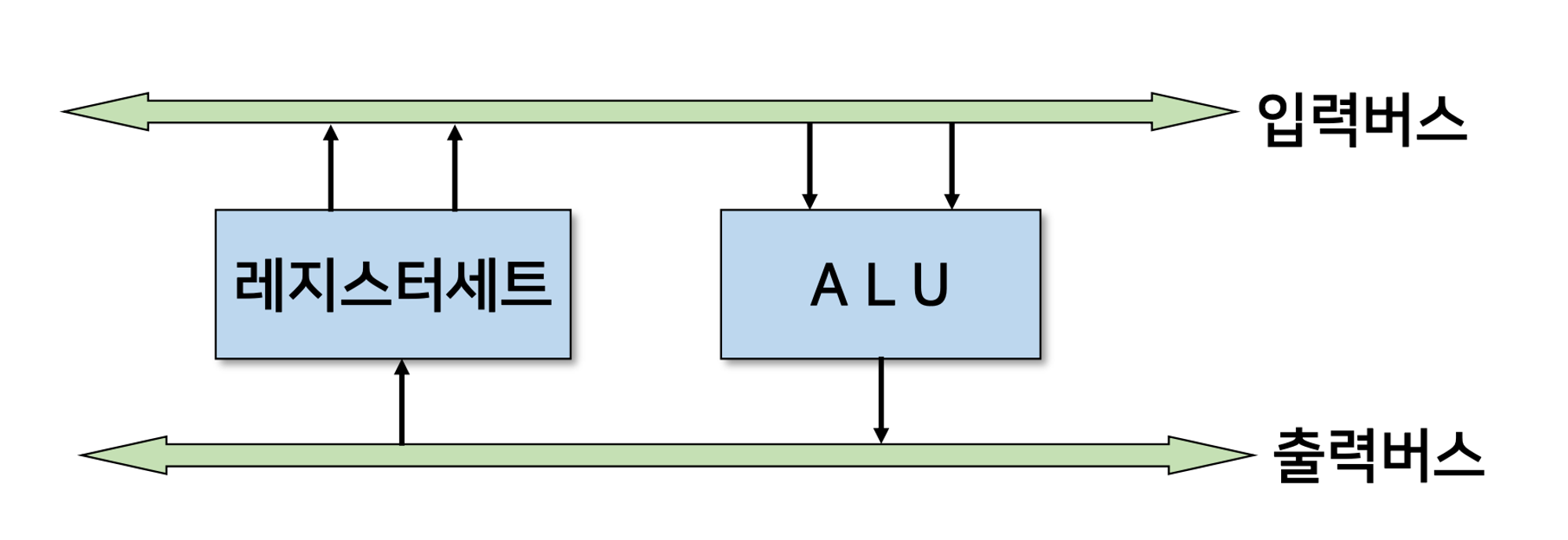

처리장치의 구성요소

- 여러 개의 레지스터(레지스터 세트)

- 산술논리연산장치(ALU)

- 내부버스(internal bus)

처리장치의 동작

마이크로 연산의 수행과정을 통해 처리장치가 동작

마이크로 연산의 수행과정

처리장치의 구성요소들의 선택신호에 의해 제어됨

- 지정된 출발 레지스터의 내용이 ALU의입력으로 전달

- ALU(ALSU)에서 그 연산을 실행

- 그 결과가 도착 레지스터에 전송

마이크로 연산의 예

- R0 ← R1 + R2

- 선택신호 A는 R1의 내용을 버스 A로 적재 - MUX 작동시킴

- 선택신호 B는 R2의 내용을 버스 B로 적재 - MUX 작동시킴

- 선태신호 F는 ALU에서 산술연산 A+B를 수행 - ALU 작동시킴

- 선택신호 H는 시프터에서 시프트 연산을 수행 - 시프터 작동시킴

- 선택신호 D는 연산결과를 R0로 적재 - 디코더 작동시킴

https://www.borntodare.me/b6e430b0-849e-4491-b0de-9cf07df49064

내부버스

레지스터들 간의 뎅이터 전송을 위한 "공통선로"의 집합

내부버스의 개념도

- 내부버스를 구성하는 방법

멀티플렉서와 디코더를 이용

- 멀티플렉서는 출발 레지스터 선택

- 디코더는 도착 레지스터를 선택

위의 그림 기준으로

4x1 멀티플렉서 4개

1x2 디코더 1개